# P3064R3: How to Avoid OOTA Without Really Trying (Informational)

Alan Stern

Paul E. McKenney

stern@rowland.harvard.edu

paulmck@kernel.org

Michael Wong

Maged Michael

fraggamuffin@gmail.com

maged.michael@gmail.com

November 15, 2025 (Post-Kona)

Audience: SG1

#### **Abstract**

The out-of-thin-air (OOTA) properties of memory\_order\_relaxed in the C++ memory model have caused considerable consternation over the years. Attempts to create memory models that rule out OOTA behaviors have been either non-executable, complex, or unloved by C++ implementers. But at the same time, we know of no instances of OOTA behavior in real C++ implementations.

We focus on shared-memory programs and C++ implementations based on traditional compilers and computing hardware, including CPUs and GPGPUs. This context permits us to consider the detailed relations between source code and machine code required by the restricted nature of volatile atomic accesses. The OOTA problem and the related challenge of coming to grips with semantic dependency are much more tractable at the hardware level than at the source level, thanks to existing formal hardware models. We show that these models' constraints prevent OOTA cycles from occurring in undefined-behavior-free C++ programs running on compiler-based implementations, provided the cycles involve only volatile atomics. We also extend this work to nonvolatile atomics by defining "quasi-volatile" behavior that we expect C++ implementations will adhere to if they perform single-thread analysis.

**Note**: Much of this paper has been superseded by P3692, so that this paper serves primarily as background material and as a repository for litmus tests. This means that the most important parts of this paper are its appendices.

## **CONTENTS**

# **Contents**

| 1 | Intr | oduction and Background                                             | 5  |  |  |  |  |  |  |  |  |  |  |  |

|---|------|---------------------------------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|--|

|   | 1.1  | What Needs to Change?                                               | 5  |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.2  | Brief OOTA Overview                                                 | 5  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.2.1 Simple OOTA Cycle                                             | 5  |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 1.2.2 Simple Reordering                                             | 7  |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.3  | Prior Work                                                          | 8  |  |  |  |  |  |  |  |  |  |  |  |

|   | 1.4  | Code-Analysis Tool                                                  | 8  |  |  |  |  |  |  |  |  |  |  |  |

| 2 | 00   | OOTA and Semantic Dependencies                                      |    |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.1  | OOTA: rf versus rfe                                                 | 11 |  |  |  |  |  |  |  |  |  |  |  |

|   | 2.2  | Properties of Semantic Dependencies                                 | 12 |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.1 Semantic Dependencies and Source Code                         | 12 |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.2 Semantic Dependencies Can Be Many-To-One                      | 12 |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.3 Semantic Dependencies Affected by Cross-Thread Optimizations  | 13 |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.4 Semantic Dependencies Affected by if Statements               | 13 |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.5 Semantic Dependencies Not Affected by if Statements           | 13 |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.6 Semantic Dependencies and Matching Up Stores                  | 14 |  |  |  |  |  |  |  |  |  |  |  |

| 3 | Wha  | at is an Execution?                                                 | 14 |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.1  | Abstract Executions                                                 | 14 |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.2  | Hardware Executions                                                 | 16 |  |  |  |  |  |  |  |  |  |  |  |

|   | 3.3  | Relation Between Abstract and Hardware Executions                   | 16 |  |  |  |  |  |  |  |  |  |  |  |

| 4 | C++  | Compilers                                                           | 18 |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.1  | Users Influence the Behavior of Compilers                           | 18 |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.2  | Global Optimization Can Destroy Dependencies                        | 18 |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.3  | Inventing Atomic Loads Can Destroy Semantic Dependencies            | 19 |  |  |  |  |  |  |  |  |  |  |  |

|   | 4.4  | Volatile and Quasi Volatile Accesses                                | 20 |  |  |  |  |  |  |  |  |  |  |  |

| 5 | Har  | dware Dependencies, Instruction Ordering, and the Fundamental Prop- |    |  |  |  |  |  |  |  |  |  |  |  |

|   | erty |                                                                     | 21 |  |  |  |  |  |  |  |  |  |  |  |

|   | 5.1  | Dependencies at the Hardware Level                                  | 22 |  |  |  |  |  |  |  |  |  |  |  |

|   | 5.2  | Instruction Ordering                                                | 22 |  |  |  |  |  |  |  |  |  |  |  |

|   | 5.3  | The Fundamental Property of Semantic Dependencies                   | 24 |  |  |  |  |  |  |  |  |  |  |  |

| 6 | A D  | efinition of Semantic Dependency                                    | 24 |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.1  | For Compilers Using Single-Thread Analysis                          | 25 |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.2  | For Compilers Using Global Analysis                                 | 26 |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.3  | Verifying the Fundamental Property                                  | 26 |  |  |  |  |  |  |  |  |  |  |  |

|   | 6.4  | Outstanding Issues                                                  | 27 |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 6.4.1 Relative versus Absolute Dependency                           | 27 |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 6.4.2 Global Analysis and Volatile versus Quasi Volatile            | 28 |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 6.4.3 Effect of Memory Layout                                       | 28 |  |  |  |  |  |  |  |  |  |  |  |

|   |      | 6.4.4 Merging Quasi-Volatile Loads                                  | 29 |  |  |  |  |  |  |  |  |  |  |  |

## CONTENTS

| 7 | Real-World Constraints307.1 Hardware Architecture and Design307.2 Constraints of the Standard327.3 Semantic Dependencies and Tooling35                                                                                                                                                                                                                                                                                                                                   |                                                                                        |  |  |  |  |  |  |  |  |  |  |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| 8 | Future Directions 36                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                        |  |  |  |  |  |  |  |  |  |  |

| 9 | Conclusion 3                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                        |  |  |  |  |  |  |  |  |  |  |

| A | Interthread Communications 38                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                        |  |  |  |  |  |  |  |  |  |  |

| В | User Influence Over Language Semantics 43                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                        |  |  |  |  |  |  |  |  |  |  |

| C | But What About Tooling?4C.1 Load/Store Ordering: Hardware View for Software Hackers4C.2 Status Quo and Focused Tooling4C.3 Change Relaxed to Forbid Load Buffering4C.4 Add Load-Store Memory Order that Forbids Load Buffering4                                                                                                                                                                                                                                          |                                                                                        |  |  |  |  |  |  |  |  |  |  |

| D | Illustrative Litmus Tests  D.1 Semantic Dependencies and volatile  D.2 Non-Trivial Semantic Dependencies  D.3 Why rfe Instead of Tried-And-True rf?  D.4 Inventing Atomic Loads  D.4.1 Illustrative Atomic-Load Invention  D.4.2 Illustrative Atomic-Load Use Invention  D.4.3 Customary Non-Atomic-Load "Invention"  D.4.4 Other Cautions for Atomic-Load Invention  D.5 Undefined Behavior and Unwise Optimization  D.6 Additional Litmus Tests                        | 49<br>50<br>57<br>65<br>65<br>67<br>71<br>72<br>73<br>75                               |  |  |  |  |  |  |  |  |  |  |

| E | Litmus Tests from "Causality Test Cases"  E.1 Causality Test Case 1  E.2 Causality Test Case 2  E.3 Causality Test Case 3  E.4 Causality Test Case 4  E.5 Causality Test Case 5  E.6 Causality Test Case 6  E.7 Causality Test Case 7  E.8 Causality Test Case 8  E.9 Causality Test Case 9  E.10 Causality Test Case 9  E.11 Causality Test Case 10  E.12 Causality Test Case 11  E.13 Causality Test Case 12  E.14 Causality Test Case 13  E.15 Causality Test Case 14 | 76<br>76<br>77<br>78<br>79<br>79<br>81<br>81<br>83<br>84<br>86<br>86<br>86<br>86<br>86 |  |  |  |  |  |  |  |  |  |  |

## **CONTENTS**

| E.16 Causality Test Case 15 |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

|-----------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|

| E.17 Causality Test Case 16 |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| E.18 Causality Test Case 17 |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| E.19 Causality Test Case 18 |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| E.20 Causality Test Case 19 |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| E.21 Causality Test Case 20 |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| F Acknowledgments           |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| G History                   |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

| References                  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |

## 1 Introduction and Background

This paper shows that compiler-based C++ implementations subject to reasonable constraints on how they treat accesses to atomic objects cannot exhibit out-of-thin-air (OOTA) cycles. It follows that these implementations need to take almost no special actions to avoid OOTA. In fact, for many compilers the constraints boil down to a simple "Don't invent or duplicate atomic accesses", which the compiler probably wouldn't do anyway.

We begin with a summary of what needs to change and a brief overview of the OOTA problem, followed by an equally brief summary of prior work in this area, and ending with a quick overview of the herd7 tool that will be used to evaluate litmus tests.

## 1.1 What Needs to Change?

What changes are needed to prevent OOTA from C++ implementations using traditional compilers and traditional hardware, including CPUs and GPGPUs?

- To the standard: No changes. The indefinite prohibition of out-of-thin-air values needs to remain.

- To implementations: No changes. Future implementations must avoid optimizations that invent, duplicate, or repurpose atomic loads. However, such optimizations must be avoided for other reasons, including preserving basic laws of arithmetic (see Appendix D.4 for more detail).

- To user code: No changes. Users must avoid undefined behavior in portable code, just as is the case now.

In short, no changes are needed because current implementations already avoid OOTA cycles. The point of this paper is to give a semi-formal demonstration of why this is the case.

## 1.2 Brief OOTA Overview

In broad terms, OOTA occurs theoretically when a group of threads load from each others' stores and each thread's store depends on the value returned by that thread's load. The collection of loads and stores forms an *OOTA cycle*. In the most extreme cases a nonsensical value can pop up "out of thin air"; however, as shown by Listing 3 below, OOTA cycles need not involve nonsensical values.

## 1.2.1 Simple OOTA Cycle

Listing 1 [19] shows a simple example where an OOTA cycle might result in all of x, y, r1, and r2 having final values of 42, despite the fact that there is nothing in the initial values or the executable code to support such an outcome:

```

1 atomic<int> x(0);

2 atomic<int> y(0);

4 void thread1()

5 {

6

int r1 = x.load(memory_order_relaxed);

7

y.store(r1, memory_order_relaxed);

8 }

9

10 void thread2()

11 {

12

int r2 = y.load(memory_order_relaxed);

13

x.store(r2, memory order relaxed);

14 }

```

Listing 1: Simple OOTA

- 1. Line 6 loads from x into r1, claiming to read the value of line 13's store rather than x's initial value and somehow obtaining 42.

- 2. Line 7 stores r1, and thus 42, to y.

- 3. Line 12 loads 42 from y to r2.

- 4. Line 13 stores 42 to x, justifying the value loaded by line 6.

Because nothing else in the C++ memory model rules out such OOTA cycles, the C++ standard explicitly prohibits them in 33.5.4p8 ([atomics.order]) [13]:

Implementations should ensure that no "out-of-thin-air" values are computed that circularly depend on their own computation.

The standard's prohibition of OOTA is of course important, for example, to prevent misapplication of the as-if rule in oracular C++ implementations, but those of us writing code in the real world must rely on actual C++ implementations. And in these implementations, this prohibition is in fact enforced by TSO ordering in strongly ordered systems and by data-dependency ordering in weakly ordered systems.<sup>1</sup>

In Listing 1 there is a *semantic dependency* from line 6 to line 7 and another from line 12 to line 13. (Roughly speaking, there is a semantic dependency from a given load to a given store when *all other things being equal, a change in the value loaded can change the value stored or prevent the store from occurring at all. Here the dependencies are trivial because the values stored simply <i>are* the values that were loaded.) Since real-world CPUs cannot store something until they have determined its value,<sup>2</sup> the stores

<sup>&</sup>lt;sup>1</sup>The need to prohibit simple OOTA is one reason why compiler-based value speculation optimizations require checks on such speculation, and these checks must be based on actual values loaded.

<sup>&</sup>lt;sup>2</sup>Another way of saying this is that real-world CPUs do not make their stores visible to other CPUs until those stores are no longer speculative. See Section 7.1 for more discussion about hardware speculation.

```

1 atomic<int> x(0);

2 atomic<int> y(0);

4 void thread1()

5 {

6

int r1 = x.load(memory_order_relaxed);

7

y.store(r1, memory_order_relaxed);

8 }

9

10 void thread2()

11 {

12

int r2 = y.load(memory_order_relaxed);

13

x.store(42, memory_order_relaxed);

14 }

```

Listing 2: Simple Reordering

in lines 7 and 13 cannot take place until the CPU knows what values are loaded by lines 6 and 12, respectively. Thus the hardware orders these stores after their corresponding loads, and this ordering prevents the OOTA result.

#### 1.2.2 Simple Reordering

It is important to distinguish true OOTA cycles from OOTA-like behavior caused by simple reordering. An example of simple reordering is shown in Listing 2 [19]. Both the C++ compiler and the CPU are within their rights to reorder lines 12 and 13, which can result in all of x, y, r1, and r2 having the value 42 as follows:

- 1. Line 13 stores 42 to x.

- 2. Line 6 loads 42 from x into r1.

- 3. Line 7 stores r1, and thus 42, to y.

- 4. Line 12 loads 42 from y to r2.

Current C++ implementations can and do exhibit this reordering behavior.

This paper will follow P2055R0 [19] in using the term *full* C++ to denote the standard including the prohibition of OOTA mentioned above. Unlike that article, we will use the term *loose* C++ (rather than *strict* C++, which seems too similar to *full* C++ for comfort) to denote a hypothetical standard that excludes this prohibition but is otherwise identical to full C++. Unqualified C++ means full C++.

The next section looks at how prior work has refined these issues.

## 1.3 Prior Work

All OOTA workers owe a debt to the foundational work in the infamous "Causality Test Cases", a version of which may be found in Appendix E.

Some executable C++ memory models correctly flag at least some executions involving OOTA cycles [2].<sup>4</sup> However, because these models are atemporal, they cannot reject OOTA executions other than by flagging the OOTA value as arbitrary, which some in fact do in at least some cases.

P0442R0 ("Out-of-Thin-Air Execution is Vacuous") [21] provided a decision procedure for classifying behaviors as permitted misordering on the one hand or disallowed OOTA on the other, using a perturbation method based on the insight that all OOTA behaviors are fixed-point computations.

Some workers recommend avoiding OOTA by forcing prior relaxed loads to be ordered before subsequent relaxed stores [7, 6, 14], but this can require real instructions be executed [17, Section 7.1], consuming real time and real electrical power to solve a strictly theoretical problem. This might have been acceptable in the 1960s of some of the authors' youths, but it is now the year 2024.

Other workers recommend various procedures to identify and avoid OOTA cycles [14, 26, 15, 3], but none of these have been looked upon favorably by C++ implementers. Some of these workers appear to have abandoned this effort, but as of early 2024, Mark Batty is persisting with modular relaxed dependencies.

Goldblatt looked at interactions between OOTA cycles and undefined behavior (UB) [10]. This document will concentrate on examples lacking UB.

All this work focused on either identifying OOTA or seeing how C++ implementations could avoid it. None applied real-world hardware ordering constraints to the problem of avoiding OOTA cycles, yet doing so might help explain why no known real-world C++ implementation results in OOTA behavior. We therefore dig more deeply into OOTA cycles in the light of these constraints.

## 1.4 Code-Analysis Tool

This paper will use the herd7<sup>5</sup> tool to analyze fragments of C++ code. This tool carries out the moral equivalent of full state-space searches of concurrent code fragments. In some cases its output will include executions with OOTA cycles, on occasion reporting undefined values for the variables involved in the cycle.<sup>6</sup>

Listing 3 shows a code fragment that under loose C++ has an OOTA cycle (although the cycle is of course prohibited in full C++). This section describes the fragment, thereby giving an overview of the herd7 tool.

The first line identifies it as a C-language litmus test and gives it a name, and this name identifies the litmus test's source file within the litmus directory in the https://github.com/paulmckrcu/oota repository. Lines 2–5 initialize variables,

$<sup>^3</sup>$ http://www.cs.umd.edu/~pugh/java/memoryModel/unifiedProposal/testcases.html.

<sup>&</sup>lt;sup>4</sup>Others cleverly avoid this issue by forbidding atomic stores of nonconstant values [4].

<sup>&</sup>lt;sup>5</sup>Available at https://github.com/herd/herdtools7.

<sup>&</sup>lt;sup>6</sup>This happens only some of the time because of idiosyncrasies in the algorithm used by herd7's self-consistency solver.

```

1 C oota-ctrl

3

[x] = 0;

[y] = 0;

5 }

7 PO(atomic int *x, atomic int *v) {

int r0 = atomic_load_explicit(y, memory_order_relaxed);

if (r0 == 42)

atomic_store_explicit(x, 42, memory_order_relaxed);

10

else

11

atomic_store_explicit(x, r0, memory_order_relaxed);

12

13 }

14

15 P1(atomic_int *x, atomic_int *y) {

16

int r1 = atomic_load_explicit(x, memory_order_relaxed);

17

if (r1 == 42)

atomic_store_explicit(y, 42, memory_order_relaxed);

18

else

19

2.0

atomic_store_explicit(y, r1, memory_order_relaxed);

21 }

2.2

23 locations[x;y]

24 exists(0:r0=42 /\ 1:r1=42)

```

Listing 3: OOTA Cycle

```

1 Test oota-ctrl Allowed

2 States 2

3 0:r0=0; 1:r1=0; [x]=0; [y]=0;

4 0:r0=42; 1:r1=42; [x]=42; [y]=42;

5 0k

6 Witnesses

7 Positive: 1 Negative: 3

8 Condition exists (0:r0=42 /\ 1:r1=42)

9 Observation oota-ctrl Sometimes 1 3

10 Time oota-ctrl 0.00

11 Hash=db3300c0e3cc86abla1477ca446dac5e

```

Listing 4: OOTA Cycle, herd7 Output

in this case setting the initial values of the global shared variables x and y to zero. (Variables that are not explicitly initialized are initialized to zero by default.) Lines 7–13 define the first thread, P0(), and lines 15–21 define the second thread, P1(). The arguments to both P0() and P1() specify which of the global shared variables each thread may access, in this case, x and y. The body of each thread contains C++ code, written in a slightly stilted manner to keep the load operations separate from the rest and because herd7's knowledge of C++ is limited.

Line 23 has a locations clause, which causes herd7 to dump out the final values of x and y. Finally, line 24 specifies an exists clause, which gives a condition to check for the final values of the specified variables. The 0: prefix denotes a variable local to P0() and the 1: prefix denotes a variable local to P1(). The / is a boolean AND, and the = signs are equality comparisons. If a variable appears in the exists clause then the final value of that variable constitutes observable behavior.

Listing 4 shows the corresponding output of the herd7 tool. Lines 3 and 4 show

<sup>&</sup>lt;sup>7</sup>The "P" stands for "process", which is herd7's name for "thread".

```

1 C simple-reordering

3

[x] = 0;

[y] = 0;

5 }

7 PO(atomic int *x, atomic int *v) {

int r1 = atomic_load_explicit(x, memory_order_relaxed);

atomic_store_explicit(y, r1, memory_order_relaxed);

10 }

11

12 P1(atomic_int *x, atomic_int *y) {

13

int r2 = atomic_load_explicit(y, memory_order_relaxed);

atomic_store_explicit(x, 42, memory_order_relaxed);

15 }

16

17 exists(0:r1=42 /\ 1:r2=42)

Analysis by "herd7 -c11 litmus/simple-reordering.litmus":

1 Test simple-reordering Allowed

2 States 3

3 0:r1=0; 1:r2=0;

4 0:r1=42; 1:r2=0;

5 0:r1=42; 1:r2=42;

6 Ok

7 Witnesses

8 Positive: 1 Negative: 3

9 Condition exists (0:r1=42 /\ 1:r2=42)

10 Observation simple-reordering Sometimes 1 3

11 Time simple-reordering 0.00

12 Hash=1b186d8f9445998c9c4ac29e062ffb74

```

Listing 5: Simple Reordering as Litmus Test

the possible states, with line 4 showing the counterintuitive outcome where both threads load the value 42. Normally these lines would include only those variables mentioned in the <code>exists</code> clause, but because of the <code>locations</code> clause the values of x and y are also listed, which can be helpful for debugging. Line 9 contains Sometimes (as opposed to <code>Never</code> or <code>Always</code>), indicating that some executions satisfy the <code>exists</code> clause and others do not.

Later examples will usually combine the litmus test and the herd7 output into one listing, as shown in Listing 5, which recasts Listing 2 into litmus-test form. Listing 1 can also be recast as a herd7 litmus test, as shown in Listing 35 on page 79. Other OOTA-related litmus tests may be found in Appendix D and Appendix E.

## 2 OOTA and Semantic Dependencies

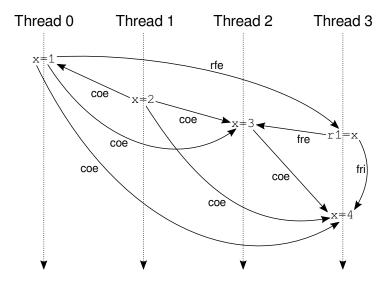

Section 2.1 demonstrates advantages of formulating an OOTA cycle as a cycle in sdep  $\cup$  rfe instead of the traditional sdep  $\cup$  rf. Section 2.2 then discusses properties of semantic dependences, showing that they are functions of executions rather than strictly of source code, among other things.

## 2.1 OOTA: rf versus rfe

Semantic dependencies form only one type of link in an OOTA cycle. The other type extends from a given store to a load that returns the value stored. It is tempting to argue that the store must precede the load in global time and combine this with the intuitive notion that any real C++ implementation must consume global time when computing a semantic dependency. This combination suggests that OOTA cycles cannot occur. The idea has been formalized by defining an OOTA cycle as a cycle in sdep  $\cup$  rf [20], where sdep is the set of semantic dependencies within each thread and rf is the set of store-to-load "reads-from" links, whether within a thread (rfi) or between threads (rfe).

This is a fine definition and is consistent with the words in the C++ standard, but it has a problem with intrathread rfi links as exemplified by the following code:

```

int r2 = atomic_load_explicit(&x, memory_order_relaxed);

atomic_store_explicit(&y, r2, memory_order_relaxed);

int r3 = atomic_load_explicit(&y, memory_order_relaxed);

atomic_store_explicit(&z, r3, memory_order_relaxed);

```

This is an elaboration of thread2 () from Listing 1 that adds z along with lines 3 and 4. The problem is that a C++ implementation may note that line 3 could well execute immediately after line 2, giving other threads no chance to modify y in between. Such an implementation might therefore behave as if the source code had instead been as follows:

```

int r2 = atomic_load_explicit(&x, memory_order_relaxed);

atomic_store_explicit(&y, r2, memory_order_relaxed);

// int r3 = atomic_load_explicit(&y, memory_order_relaxed);

atomic_store_explicit(&z, r2, memory_order_relaxed);

```

Here line 3 has been optimized away in favor of line 4 storing the same value to z that was stored to y by line 2. And given that the load from y no longer exists, it cannot possibly act as a temporal constraint.

In order to avoid these rfi links we will substitute rfe for rf, defining an OOTA cycle—for now—as a cycle in sdep  $\cup$  rfe. Any rfi links in a cycle can instead be interpreted as part of sdep. Although this does shunt additional complexity onto the term "semantic dependency", it also enables us to cleanly separate the interthread and intrathread portions of any given OOTA cycle.

The inability of rfi links to act as temporal constraints is not the only, or even the main, weakness in the intuitive argument against OOTA cycles. The primary difficulty lies in the fact that the code transformations performed by optimizing compilers can destroy dependencies, including semantic ones (depending on one's definition). That is, even when the potential for a dependency exists in the source code for a thread, there might be no dependency in the machine code produced by a compiler. There would then be no constraint forcing the implementation to execute the thread's store later in global time than the load it supposedly depends on, and thus no impediment to the occurrence of an OOTA cycle. We will see examples of this destruction in Sections 4.2 and 4.3 below.

<sup>&</sup>lt;sup>8</sup>See Appendix A for definitions and properties of rf, rfe, and rfi.

## 2.2 Properties of Semantic Dependencies

This section uncovers some semantic-dependency complexities. Section 2.2.1 shows that semantic dependencies are functions of executions, rather than being strict functions of the source code. Section 2.2.2 shows that semantic dependencies do not necessarily extend from a single load to a single store, but can instead involve multiple loads. Section 2.2.3 shows that semantic dependencies can be affected by cross-thread optimizations. Sections 2.2.4 and 2.2.5 show that if statements can have surprising effects on semantic dependencies, up to and including eliminating them completely. Finally, Section 2.2.6 demonstrates some challenges in determining which of a group of stores is involved in a given semantic dependency.

#### 2.2.1 Semantic Dependencies and Source Code

Some discussions of semantic dependencies assume that they are strictly functions of the source code. Although there are ways of making this work, many instances of semantic dependency must be considered functions of particular executions. Consider for example:

$$x = y * z;$$

(Here and below, we have written shared-variable accesses without annotations, for brevity. Please imagine they are all relaxed atomic.)

As long as z is zero, changes in the value of y will not cause a change in the value stored to x. As a result, the semantic dependency from y to x exists only in executions where z is nonzero, which shows it is a property of the execution, not just of the source code.

## 2.2.2 Semantic Dependencies Can Be Many-To-One

Suppose that in some execution of the previous example, both y and z are zero. Then changes to either y or z will not cause a change in the value stored to x. In other words, in this execution there is no semantic dependency from either y or z to x. But there is a semantic dependency from the pair  $\{y, z\}$  to x, because changes to both y and z can cause the value stored in x to change. This means that, prior work [21] notwithstanding, accurate definitions of sdep cannot always rely on single-variable perturbations; they must consider changes to multiple variables. See Appendix D.2 for examples and additional discussion.

Since we can no longer regard sdep as always relating a single load to a store, the notion of a cycle involving sdep appears problematic. We are forced to change our definition of an OOTA cycle again; we will say that an execution is an instance of OOTA if in that execution:

There are stores  $W_0, \ldots, W_m$ , where each  $W_i$  semantically depends on a set of loads  $\{R_{i,0}, \ldots, R_{i,n_i}\}$ , such that each  $R_{i,j}$  reads from one of the  $W_k$  stores in a different thread.

This makes OOTA more complicated than a simple cycle but we will continue to refer to "OOTA cycles" out of habit. Note that this new definition includes and generalizes the earlier "cycle in sdep  $\cup$  rfe" definition.

## 2.2.3 Semantic Dependencies Affected by Cross-Thread Optimizations

Consider the following:

$$x = y - z$$

;

There appear to be semantic dependencies from y to x and from z to x. However, if the implementation somehow knows that y is always equal to z at this point then there is no semantic dependency; the implementation can act as if the statement were simply "x = 0". We leave aside the question of how the implementation would know this, given that y and z cannot be updated simultaneously and are subject to change at any time by other threads (a point we will return to in Section 4.2).

#### 2.2.4 Semantic Dependencies Affected by if Statements

Consider the following if statement:

```

r1 = x;

if (r1 > 0)

y = r1;

else

z = r1;

```

Here there is a semantic dependency from x, but in some executions it extends to y and in others to z. This is an example of a load affecting not the value of a given store, but rather whether or not that store is executed at all.

## 2.2.5 Semantic Dependencies Not Affected by if Statements

Compare this example to the previous one:

if

$$(x > 0)$$

$y = 42;$

else

$y = 42;$

Because the stores executed on each arm of the if statement write identical values to identical addresses, one could equally well regard the two statements as performing two different stores or as performing for all intents and purposes a single store, independent of x. Reasonable C++ implementations might disagree on this matter and therefore on whether or not the example has a semantic dependency. It is the implementation's choice.

<sup>&</sup>lt;sup>9</sup>At least not by any means within the confines of the standard.

## 2.2.6 Semantic Dependencies and Matching Up Stores

Suppose we take the view that the previous example involves only one store. This opens up the door to greater complexity:

```

if (x > 0) {

L1: y = 42;

} else {

y = 53;

y = 42;

}

```

Consider an execution in which x is greater than zero, so the statement labeled L1 runs. Is it semantically dependent on x? The answer isn't immediately clear. If the other arm of the if is taken then a store of the same value 42 to y occurs, but 53 is written before it. Which of these two stores should be compared with the store in L1?

One way to cut the Gordian knot is to match up the stores by the order they occur: Since  $\mathtt{L1}$  is the first store to  $\mathtt{y}$  in its arm of the  $\mathtt{if}$  statement, it should be matched up with the first store to  $\mathtt{y}$  in the other arm. Those two stores write different values so there is a semantic dependency.

On the other hand, a compiler may decide to drop the y=53 store entirely, leaving it out of the machine code, on the grounds that it's always possible for the two adjacent stores to y to execute in such quick succession that no other thread manages to read the value 53 before it gets overwritten with 42. If the compiler does this then the first store to y in that arm of the if statement would agree with the store in L1, and so there would not be a semantic dependency. Once again, the decision is up to the implementation.

We have seen several examples showing that semantic dependencies may vary according to the execution and even the implementation. This raises several questions, of which the first is: What exactly is an execution?

## 3 What is an Execution?

This section looks more carefully at executions, in some cases revisiting example code from Section 2.2. Section 3.1 looks at executions from the viewpoint of the abstract machine, and Section 3.2 looks at them from the viewpoint of the computer hardware. Finally, Section 3.3 describes how to relate these two viewpoints.

## 3.1 Abstract Executions

The C++ standard describes the execution of a program in terms of "a parameterized nondeterministic abstract machine" in 4.1.2p1 ([intro.abstract]). This description specifies how the abstract machine carries out the operations of a source program in great, but not complete, detail:

• Some of the abstract machine's characteristics are implementation defined, including things like the number of bits in the various integer types or whether the char type is signed.

- Some aspects of an execution are unspecified or nondeterministic, including things like the order of evaluation of the operands of most binary operators or of the arguments in a function call. Implementations may choose from a set of allowed behaviors.

- Some actions are deemed to have undefined results; the standard says essentially nothing about programs that can give rise to undefined behavior.

- Asynchronous actions (i.e., signal handlers) are largely ignored.

- Input and output are not described in any detail.

In addition to these points, the standard does not specify which store an atomic load must read from, beyond requiring that the overall pattern of loads and stores be consistent with the C++ memory model. We assume that programs will not indulge in any computations that could vary spontaneously from one execution to another, such as basing a dependency on the time of day or a process ID.

The implementation-defined aspects can affect whether or not an abstract execution contains a semantic dependency. As an example consider the following, where the type of c is char:

```

y = (c >= 0);

```

Here y is semantically dependent on c in executions running on implementations in which char is a signed type, but not those for which it is unsigned.

The same is true for the nondeterministic aspects of an execution. Consider this example, with  $\dot{\mathbf{1}}$  initially zero:

```

int foo(int a, int b)

{

return a / b;

}

r1 = foo(++i, ++i);

x = r1 * z;

```

Because early C implementers could not come to agreement, the standard does not specify the order of evaluation of function arguments, so the value calculated for r1 might be zero (1/2 truncated) or two (2/1). In the former case there is no semantic dependency from z to x, but in the latter case there is.<sup>10</sup>

(According to the current version of the standard, conflicting side effects in unsequenced subexpressions constitute undefined behavior, although there are proposals to make them defined in both C++ [25] and C [8]. Nevertheless, the example above is allowed because the order of evaluation of arguments to a function call is "indeterminately sequenced"  $(7.6.1.3p7 \ [expr.call])$  rather than unsequenced, a subtle distinction.)

The abstract executions we use will be fully specified. This means that all the missing information must be supplied: the implementation-defined characteristics, the

<sup>&</sup>lt;sup>10</sup>Thanks to Peter Sewell for pointing out this possibility.

selections for the nondeterministic pathways, and most notably, for each load, the store from which it reads and the value of the load. We ignore issues of signal handlers and I/O; in any case our litmus-test programs don't use them (but see the discussion of volatile loads in Section 3.3 below). The totality of this information—along with the program's source code, of course—determines within each thread a unique, linearly ordered series of steps to be carried out by the abstract machine. However, with a few exceptions<sup>11</sup> there is no ordering relation between steps carried out in different threads. Even if a relaxed atomic load in one thread reads from a relaxed atomic store in another thread, the standard does not require the store to come before the load in any meaningful way.

With the compiler-based implementations we are considering, the choices for the nondeterministic pathways are "frozen" into the machine-code executable file and thus are completely determined at runtime. A consequence of this is that if two abstract executions of the same thread under the same implementation agree on the values obtained by the load operations during their first *N* steps then they will agree in every respect during those steps, although they may diverge later.

#### 3.2 Hardware Executions

The outcome when a given computer executes the machine code in a file has historically been much better defined than the executions of the C++ abstract machine. The hardware's behavior is typically specified with great precision by the designer or manufacturer, and there are formal, executable memory models describing exactly what patterns of loads and stores can occur. Thus, leaving aside questions of asynchronous interrupts and system calls, the behavior of a CPU executing a particular thread within a program is entirely determined by the values obtained by the various memory-load instructions.<sup>12</sup>

For this reason, the hardware executions we use will comprise (along with the machine code being run) the computer architecture and for each load instruction, the store instruction from which it reads and the value obtained. At this level, the fact that the original program was in C++ is irrelevant; the same concepts apply to the execution of a program in any compiled language.

A computer may execute the instructions in a thread out of order. The architecture specifies the extent to which this may happen, and it also specifies circumstances under which some pairs of instructions must be executed in order. Nevertheless, we will consider an execution to be determined by the values obtained by its loads. As with abstract executions, if two hardware executions of the same thread on the same type of computer agree on the values obtained by the load instructions during their first *N* steps then they will agree in every respect during those steps, although they may diverge later.

#### 3.3 Relation Between Abstract and Hardware Executions

The C++ standard requires that for any valid implementation, when a program runs its observable behavior must be the same as that of some abstract execution of the

<sup>&</sup>lt;sup>11</sup>Such as a load-acquire synchronizing with a store-release.

<sup>&</sup>lt;sup>12</sup>We regard read-modify-write instructions as consisting of both a memory load and a memory store.

source code given the same input (in the absence of any abstract executions containing undefined behavior).<sup>13</sup> This means:

- The program's output must be the same as that of the abstract execution.

- Volatile accesses "are evaluated strictly according to the rules of the abstract machine" (4.1.2p6.1 [intro.abstract]).

- (There is a condition on the timing and interleaving of input and output, which does not matter for our purposes.)

We will say that the abstract execution is *realized by* the hardware execution.

Under any particular implementation, a single program can have many different abstract executions, varying in their decisions about which store each load reads from and thus the value obtained. It's worth noting, however, that not all the possible abstract executions of a program need be realizable by the machine-code executable file produced by that implementation. In fact, we will see that *none* of the possible OOTA executions allowed by the loose C++ abstract machine will ever be realized by the executables produced by many compilers,

Exactly what the standard's restriction on volatile accesses means isn't entirely clear. The handling of volatiles, as understood by compiler developers, has been described as more folklore or a gentlemen's agreement than anything else. To help guide C++ users and implementers, the standard adds these suggestive comments (9.2.9.2p5 and 6 [dcl.type.cv]):

The semantics of an access through a volatile glvalue are implementation-defined.

volatile is a hint to the implementation to avoid aggressive optimization involving the object because the value of the object might be changed by means undetectable by an implementation.

Taking our cue from the folklore, we propose to recognize formally that programs with volatile objects can execute in two different kinds of environment: a benign one in which accesses to these objects work the same as nonvolatile memory accesses, and a nonbenign one in which accesses to volatile objects are subject to outside interference and act more like I/O. In particular, when it runs in a nonbenign environment, a program's volatile loads can return unpredictable values. They don't necessarily read from stores (in contrast to nonvolatile loads, which always must return the value of the store they read from). This implies that volatile load-acquires do not synchronize with volatile store-releases in the sense of the C++ memory model, <sup>14</sup> so they do not contribute to the happens-before relation. Also, in these environments the rfe relation does not apply to volatile loads and stores, and hence the accesses in an OOTA cycle must be nonvolatile.

Of course, the machine-code file produced by a compiler must work properly in either kind of environment. Therefore the compiler must generally treat accesses to

<sup>&</sup>lt;sup>13</sup>This requirement is the standard's "as-if" rule.

<sup>&</sup>lt;sup>14</sup>However, they might instead synchronize with store-releases in device firmware (or vice versa), roughly speaking.

volatile objects as a form of I/O, and it may not invent, omit, merge, or reorder these accesses, as we will discuss in Section 4.4 below.

Given this relation between abstract and hardware executions, it is time to turn our attention to the tools that manage hardware executions so as to enforce that relation, namely, compilers.

## 4 C++ Compilers

A complete C++ implementation consists of much more than just a compiler. Among other things, for example, it might have a collection of . h header files, a linker, runtime libraries, and a dynamic loader. Nevertheless, for our purposes the compiler is the most important component because it is what primarily determines the translation from a C++ source program to directly executable machine code. We will therefore use the terms "compiler" and "implementation" interchangeably.

Section 4.1 shows that C++ compilers can be influenced by their users as well as by the standard. Section 4.2 presents an example showing that global optimizations can destroy semantic dependencies, and then Section 4.3 analyzes examples showing that inventing atomic loads can destroy semantic dependencies. Section 4.4 then presents required properties of volatile atomic operations, and also defines properties of quasi-volatile atomic operations.

## 4.1 Users Influence the Behavior of Compilers

The exact definition of a computer language is a subject of some debate, with standards, implementations, and users all having some degree of influence [23, 24], and each being prone to change over time. In areas that are not well settled or where users might reasonably want to resist the dictates of the standard, compilers often provide switches to override their default behaviors. An example is GCC's -funsigned-char command-line argument, which causes it to treat variables of type char as unsigned. More examples of user control over language semantics are given in Appendix B and by the discussion in [23, 24].

We will consider these user-specified compiler switch settings to fall within the implementation-defined parameters of the C++ abstract machine. They should be provided, implicitly or explicitly, as part of any abstract execution.

## 4.2 Global Optimization Can Destroy Dependencies

Recall the Simple OOTA example in Listing 1 on page 6, in which thread1 () loads the value of x and stores it in y while thread2 () does the reverse. A globally optimizing loose C++ compiler given that program might transform it to the following before translating it into machine code, if the compiler is sufficiently perverse:

```

1 atomic<int> x(0);

2 atomic<int> y(0);

3

```

```

4 void thread1()

5 {

6    int r1 = 42;

7    y.store(r1, memory_order_relaxed);

8 }

9

10 void thread2()

11 {

12    int r2 = 42;

13    x.store(r2, memory_order_relaxed);

14 }

```

The loads previously on lines 6 and 12 have been replaced by constants. Such a transformation complies with the loose C++ standard, even though the resulting executable file would produce an unintuitive OOTA outcome every time it runs!

The only justification a compiler could have for generating output like this is that it knows exactly what accesses will be performed by both threads, and therefore it knows that it will not violate the loose C++ memory model by assuming each thread's load reads from the other's store. A similar justification can underlie the reasoning in Section 2.2.3; in principle an analysis of the complete program could lead a compiler to conclude that y will always be equal to z whenever a particular y - z expression is evaluated, allowing the compiler to replace the expression with a constant 0.

By contrast, a compiler that analyzes only one thread at a time when performing its optimizations and other code transformations will not have this kind of global knowledge, and consequently it would not perform the OOTA-ful transformation shown here.

Because we seek to find characteristics of compilers that will guarantee the absence of OOTA behavior in the machine code they generate, we will for now confine our attention to compilers that analyze only one thread of source code at a time. In more precise terms, we want the compilers under consideration always to generate the same machine-code output for threads having the same source code, regardless of the rest of the code in the programs containing those threads. Later on we will return to globally optimizing compilers.

## 4.3 Inventing Atomic Loads Can Destroy Semantic Dependencies

Consider this code, in which the final values of r1 and r2 are observable:

```

int r1 = (x != 0);

int r2 = (y != 0);

z = (r1 == r2);

```

It is clear that the store to z semantically depends on the load from y, because the value of z will change whenever y changes between zero and nonzero (all else being equal).

However, an especially devious compiler might transform the source into the following form before translating it to machine code:

<sup>&</sup>lt;sup>15</sup>A less perverse compiler could choose to avoid the OOTA cycle simply by not making this transformation.

```

int r1;

2

int r1a = (x != 0);

int r1b = (x != 0);

int r2 = (y != 0);

4

5

if (r1a != r1b) {

6

r1 = r2;

7

z = 1;

8

} else {

9

r1 = r1b;

10

z = (r1 == r2);

11

```

The idea is that r1a, r1b, and r2 can each be only zero or one, so if r1a and r1b differ then one of them must be equal to r2. In executions where this happens—because another thread writes to x between the two loads—the implementation can choose at runtime to use for r1 whichever value agrees with r2, as shown on line 6. Then the value stored to z on line 7 will always be one, with no dependence on the value loaded from y.

A noteworthy aspect of this transformation is that it invents an atomic load: The original form of the code reads x only once, whereas the transformed code reads it twice. Therefore we can rule out transformations like this one by insisting the compiler not invent (or duplicate) atomic loads. In fact, we will require that atomic accesses be treated as "quasi volatile", in that the compiler is allowed to omit, merge, or reorder them but not invent them.

Just what does this mean?

## 4.4 Volatile and Quasi Volatile Accesses

Declaring objects to be volatile is a way for the programmer to indicate that the hardware should perform all accesses to these objects exactly as written in the source code, perhaps because they represent memory-mapped device registers or DMA buffers rather than normal memory locations. In any event, we expect compilers' translations of volatile-object accesses into machine code to be as close to verbatim as possible.

To express this idea in more formal terms, and to explain what we mean by "quasi-volatile" object accesses, we augment the requirements for a hardware execution H to realize an abstract execution A. Each realization must include a map from the set of accesses of volatile objects in A to the set of instructions in H that access these objects, having the following properties:

- The map connects accesses of the same type (loads to loads and stores to stores) and to the same object.

- The map connects accesses in a thread of A to accesses in the corresponding thread of H.

<sup>&</sup>lt;sup>16</sup>This issue is discussed more fully in Appendix D.4, which includes other examples of invented atomic loads leading to incorrect behavior, that is, behavior not exhibited by the abstract machine. See also the "Invented Atomic Loads" paragraph of Section 7.2.

- The map is value-preserving: The value of an access in A must be the same as the value of the access it maps to in H.

- In benign environments the map must preserve the rf relation. That is, if volatile load *R* in *A* reads from store *W* then then the instruction it maps to in *H* must read from the instruction that *W* maps to.

- The map is order-preserving: Two accesses in the same thread of *A* must map to accesses occurring in the same order in *H*. (In other words, the compiler may not reorder accesses to volatile objects.)

- The map is onto: For every access in *H* to a volatile object there must be an access in *A* that maps to it. (In other words, the compiler may not invent accesses to volatile objects.)

- The map is one-to-one: Different accesses in A map to different accesses in H. (In other words, the compiler may not merge accesses to volatile objects.)

- The map is total: Every access in A to a volatile object maps to some access in H. (In other words, the compiler may not omit accesses to volatile objects.)

Most of these are direct consequences of the fact that volatile-object accesses are considered to be a form of I/O when the program runs in a nonbenign environment. But to be clear, these requirements apply in all environments.

By contrast, accesses to quasi-volatile objects are normal memory accesses, not subject to unpredictable interference in nonbenign environments (otherwise the program's behavior would be undefined). However, we do impose most of the requirements above on quasi-volatile object accesses. The last two bullet points are left out: Compilers are allowed to merge or omit accesses to these objects. Because of this, the bullet point about preserving the rf relation applies only when *R* is not omitted, in which case *W* must not be omitted either, but now it applies in all environments. Lastly, the requirement for order preservation is weakened; it applies only to pairs of accesses to the same quasi-volatile object. Accesses to different objects may be reordered relative to each other.

Section 7.2 presents examples illustrating some of these requirements.

# 5 Hardware Dependencies, Instruction Ordering, and the Fundamental Property

Section 5.1 discusses hardware-level dependencies involving machine instructions. Section 5.2 then examines the relationships between various instruction-ordering mechanisms and semantic dependencies. This material feeds into Section 5.3, which presents the fundamental property of semantic dependencies and related complications.

## 5.1 Dependencies at the Hardware Level

Dependencies between machine instructions can be understood in terms of the flow of information within a CPU. Each instruction has a set of inputs and is the source of a set of outputs, some of which flow to the inputs of later instructions. The inputs determine what an instruction will do. A few examples:

- An add instruction would typically have two inputs (the register values to be added together) and two outputs (the sum to be stored in a general-purpose register and some condition-code bits—e.g., Zero, Carry, and Overflow—to be stored in a status register).

- A conditional-move instruction would have as inputs the condition-code bits to

test, the source register value, and the target register value; the output would be

the value to be stored in the target register.

- A conditional- or computed-branch instruction would have as inputs the conditioncode bits to test, the address of the following instruction (to be used if the condition

is false) and the destination address (to be used if the condition is true). The

output is the new address to be written to the instruction-pointer register.

- A memory-load instruction's input is the address to load from, and its output is the value obtained by the load, to be stored in a register.

- A memory-store instruction's inputs are the value to store and the address at which to store it; there are no outputs.

Note: Hardware dependency analysis considers only the information flowing *within* a CPU, not information flowing between the CPU and memory, which is handled separately as part of the action taken by an instruction.

Using this scheme, we say that an instruction J is dependent on another instruction I when any of I's outputs flow into J's inputs, perhaps indirectly via some intermediate instructions. Tracing back the flow of information between instructions, you can see that any hardware dependency must ultimately emanate from a load instruction or the thread's initial register values (or possibly some sort of input instruction, but we will not consider that complication here). These are the only sources of truly new information in a thread.

The concept is simple, but it is important because of the way dependencies affect instruction ordering in weakly ordered architectures.

## **5.2** Instruction Ordering

A CPU may start executing an instruction speculatively, but at some point it must *commit* to a decision either to definitely execute the instruction's action with some collection of well defined inputs and outputs or else to abandon it. Thanks to the law of cause and effect, a CPU is not able to commit an instruction or its outputs until the relevant inputs' sources have committed. The reason is obvious: An input is subject to change at any time until its source commits to its value, and the instruction and its outputs

can't commit until the CPU has fully determined what it will do and what they will be. (On the other hand, the CPU need not wait for inputs that won't affect the instruction's results. For instance, a conditional-move instruction wouldn't need to wait for the source register input to be determined once it knew that the condition was definitely false. And, although no architectures we are aware of do this, there is nothing in principle to prevent a CPU from committing a multiply instruction as soon as either one of its inputs' sources has committed to the value zero.)

Of course, an instruction's inputs don't all have to be outputs from earlier instructions; some of them may be immediate constants present in the instruction itself. In this case there is no need to wait for those inputs because their values are fully determined from the start.

The overall effect of these hardware dependencies is that if a change to an output of instruction I would lead to a change in the action or outputs of a later instruction J, then the CPU must commit I's output before committing J's action and outputs. Thus dependencies force instructions to commit in order, even on weakly ordered architectures.

We will say that one instruction is *ordered after* another to mean that the CPU forces it to commit after the other one commits. Hence instructions are ordered after the instructions they depend on. (Note that this implies nothing about when a load instruction retrieves its value from memory; it may do so long before it or a prior instruction commits.)

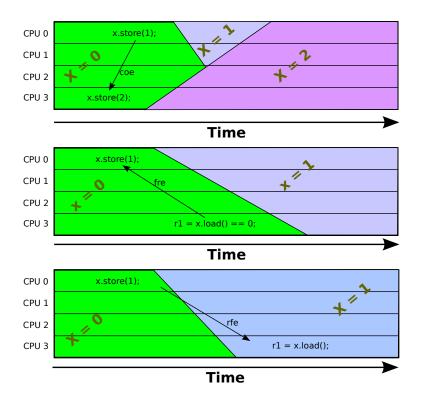

Dependencies aren't the only mechanism that can lead to ordering in hardware executions. The simplest alternative is a load reading from a store in another thread, i.e., the rfe relation. As mentioned in Section 1.2.1, a CPU does not make the value of a store instruction available for other CPUs to load until the store commits or some time later. And after this happens, it takes some time for the information about the store to travel from that CPU to others, owing to the inescapable facts that processors have nonzero size and information cannot travel faster than the speed of light. Since the load instruction cannot commit until its output (the value it reads) is fully determined, it must commit after the store it reads from. (To be fair, this should be considered more as a *result* of ordering than as a *cause* of ordering, in that if a load commits before a store on another thread then it cannot possibly read from that store.)

A similarly straightforward mechanism for ordering is conditional or computed branches. An instruction executing after such a branch cannot commit until the CPU has committed to whether the branch will be taken and if taken, where it will branch to (that is, the output value it will send to the instruction-pointer register); until then the CPU cannot know whether the later instruction should be executed at all. Therefore instructions following a conditional- or computed-branch instruction in a hardware execution must commit after the branch, and hence after the source for the branch's condition or destination input. (There could theoretically be an exception for a branch that conditionally jumps to the immediately following instruction. We can ignore this possibility by treating such branches as no-ops.)

## 5.3 The Fundamental Property of Semantic Dependencies

With the contents of the last few sections under our belts, we can formulate the Fundamental Property that we would like all semantic dependencies to satisfy. Note that this formulation makes sense only for implementations in which all atomic objects are treated as volatile or quasi volatile.

Let W be a store which semantically depends on loads  $\{R_0, \ldots, R_n\}$  in some abstract execution A, and suppose that W is not omitted in some hardware execution H realizing A. Then for some i, load  $R_i$  is not omitted in H and the instruction it maps to is ordered before the instruction W maps to

It's quite straightforward to show that under any implementation in which semantic dependencies satisfy the Fundamental Property, no OOTA cycle has a nontrivial realization.

Indeed, suppose that abstract execution A is realized by hardware execution H and A has an OOTA cycle. This means there are atomic stores  $W_i$  in A, semantically depending on atomic loads  $\{R_{i,j}\}$  where each of the loads reads from one of the  $W_k$  stores in a different thread. Let  $W_i'$  and  $R_{i,j}'$  be the hardware instructions these accesses map to in H, if they aren't omitted. Assuming that the stores are not all omitted, one of the  $W_i'$  instructions, let's say  $W_0'$ , must commit first. By the Fundamental Property, one of the loads that  $W_0$  depends on, let's say  $R_{0,0}$ , is not omitted and  $R_{0,0}'$  is ordered before  $W_0'$ . But now we have a contradiction:

- $W'_0$  commits after  $R'_{0,0}$ ;

- $R'_{0,0}$  commits after the store instruction  $W'_k$  it reads from;

- $W'_{\nu}$  commits no earlier than  $W'_{0}$ .

If all the stores in the OOTA cycle are omitted then all the reads must be omitted as well. In effect, the entire cycle has been optimized out of existence by the compiler. Although we are unable to prove it, we conjecture that in this situation there must be another abstract execution which has the same observable effects as *A* and is also realized by *H*, but in which the OOTA cycle does not occur. Thus there would be no way to tell, merely by observing the effects of *H*, whether there was an OOTA cycle or not. For this reason we declare realizations of OOTA cycles in which all the accesses are omitted to be *trivial*.

## 6 A Definition of Semantic Dependency

Semantic dependency is a notoriously difficult concept to define rigorously and precisely. A large part of the reason is because it was never a completely clear concept to begin with, especially when there are multiple accesses to the variables involved. In this section we will stick our necks out by offering just such a definition. No doubt many people will object to it for various reasons, but we nevertheless hope it will help move the discussion forward.

The definition given below is applicable only to C++ implementations that treat all atomic objects as though they are volatile or quasi volatile. (For compilers that perform only single-thread analysis, not global analysis, quasi volatile is sufficient.) In this setting we can relate abstract and hardware executions by means of the map of accesses described in Section 4.4. The key insight is that this allows us to consider semantic dependencies at the level of the machine code, where they are much more tractable.

Section 6.1 focuses on compilers that restrict their analysis to a single thread, Section 6.2 relaxes this single-thread restriction, Section 6.3 verifies the fundamental property of semantic dependencies, and Section 6.4 discusses general questions regarding our definitions.

## **6.1** For Compilers Using Single-Thread Analysis

In this section we consider implementations whose compilers perform only single-thread analysis and treat atomic objects as quasi volatile. This implies that if two different programs contain the same thread (i.e., the same source code for the functions and objects in the thread), the machine code generated by the compiler for the thread will be the same in the two programs.

We begin by recognizing that semantic dependencies are relative to a particular execution and a particular implementation, as described in Section 2.2. The same source code may or may not contain a semantic dependency, according to the details of the execution in question and the machine code produced by the compiler. For this reason we will characterize semantic dependencies in a given abstract execution realized by a given hardware execution. (While it possible to argue about semantic dependencies in abstract executions that have no hardware realizations, doing so seems pointless.)

Let A be an abstract execution of some program P containing a thread T, and let H be a hardware execution realizing A. Let W in T be a store to an atomic object, and let  $\{R_0, \ldots, R_n\}$  in T be a set of loads from atomic objects on which W might or might not depend. We can dispose of one case immediately: If W is omitted in W then the issue of semantic dependency is moot. You can give either answer since it will have no effect. Therefore we'll assume that W is not omitted. Then:

There is a semantic dependency from  $\{R_i\}$  to W in A and H, relative to the compiler used to produce H, if there is another abstract execution B realized by hardware execution G under the same compiler that together witness the semantic dependency.

To be a proper witness, B must be an execution of some program Q, not necessarily the same as P but which contains the same thread T. The thread should start out with the same initial state in A and B, and all loads in A coming before any of the  $R_i$  should obtain the same value as they do in B (this is part of our interpretation of "all else being equal"). It follows that the two abstract executions of T will be identical up to the first of the  $R_i$  loads.

Let W' and  $\{R'_i\}$  be the accesses in H that W and the non-omitted  $\{R_i\}$  loads map to. We then require that the hardware executions of T in H and G be identical for an initial period lasting up to the first of the  $R'_i$ . Following this initial period there will be a common period, during which H and G execute the same machine instructions but

do not necessarily compute the same values. This common period ends when one of the hardware executions takes a conditional branch that the other doesn't, or when a computed branch leads to different addresses in the two executions, or when T ends, whichever comes first. Past this point H and G diverge and are no longer directly comparable, as they execute different instructions. Our third requirement for being a witness is that each load in the common period either must obtain the same value in H and G, or must itself be one of the  $R_i'$  loads, or must be ordered in H after one of the  $R_i'$  loads (this is the remaining part of our interpretation of "all else being equal".)

Finally, we need to determine an instruction X' in G that corresponds to W'. If W' is in the initial or common period of H this is no problem; we can take X' to be W' itself. But if W' is in the divergent part of H then things aren't so simple. The choice is somewhat arbitrary, and so we will fall back on the earlier proposal of matching up stores by the order they occur. Let y be the atomic object that W' stores to, and suppose W' is the Nth store to y within the divergent part of H. Then X' will be the Nth store to y in the divergent part of G, if such a store exists. Our last requirement for being a witness to a semantic dependency is that X' act differently from W': it doesn't exist, it stores a different value, or it stores to an object other than y.

## **6.2** For Compilers Using Global Analysis

As promised earlier, we now consider implementations whose compilers may use global analysis. In order to obtain the desired results we have to require that these compilers treat all atomic objects as volatile. Equivalently, the machine code generated by such a compiler must be the same for a given program as for a "volatilized" form of the program in which all the atomic objects are defined to be volatile.

In this context our definition of semantic dependency is essentially the same as before. Since we can no longer expect the machine code for a thread to be the same regardless of the program it belongs to, the program Q in the earlier definition (of which B and G are executions) must be P or its volatilized form. However, we do now allow the possibility that the executions B and G take place in a nonbenign environment. Aside from these minor adjustments, the definition remains unchanged.

## **6.3** Verifying the Fundamental Property

Of course we want to check that our definition of semantic dependency satisfies the Fundamental Property of Section 5.3. Given the information we have already presented, the demonstration is easy.

Suppose we have W,  $\{R_i\}$ , A, and H as in the definition. The Fundamental Property assumes that W is not omitted in H, so there is an abstract execution B with hardware realization G witnessing the semantic dependency of the store W on the loads  $\{R_i\}$  in A and H. We must show that some  $R_i$  is not omitted and  $R_i'$  is ordered before W' in H. The proof splits into three cases.

First case: W' lies in the initial period of H. During the initial period of the hardware executions, H and G behave identically and therefore W' performs the same write in both. This contradicts the fact that B and G witness the semantic dependency.

Second case: W' lies in the common period of H. Since the action of W' in H is different from its action in G, at least one of its inputs must differ between the two hardware executions. Therefore the source instruction for that input must behave differently, and so must one of its sources, going back until we reach a load instruction that obtains differing values in H and G. Then W' depends on this load and so is ordered after it. And since the load must lie in the common period of H, by the definition of semantic dependency it must either be one of the  $R'_i$  or be ordered after one of them. Therefore W' is ordered after one of the  $R'_i$  in H, which certainly means that  $R_i$  is not omitted.

Third case: W' lies in the divergent part of H. This happens when W' comes after the conditional or computed branch which marks the end of the common period by going different ways in H and G. Just as in the previous case, since the branch behaves differently in the two executions it must be ordered after one of the  $R'_i$  loads. And then so must W', because any instruction following a conditional- or computed-branch instruction must commit after the branch commits. QED.

A corollary of this result is that if an implementation's compiler either

- uses single-thread analysis and treats atomic objects as quasi volatile, or

- uses global analysis and treats atomic objects as volatile,

then programs produced by that implementation will never exhibit OOTA. Thus the implementation will automatically comply with full C++, even though it may be been designed only to comply with loose C++.

## 6.4 Outstanding Issues

Here we consider some general questions related to our definition of semantic dependency.

## 6.4.1 Relative versus Absolute Dependency

A drawback of the definition is that it is only relative to a specific compiler or implementation. This may strike some people as wishy-washy and avoiding the real problem, in that a given piece of code should either contain or not contain a semantic dependency, independent of the implementation used to run it.

We can address this drawback by defining an *absolute semantic dependency* as one that is present relative to any valid loose C++ implementation, past, present, or future, real or imagined. Of course this notion has its own problems, including that it is extremely nonconstructive and impossible to apply in practice. However it may be the best we can do with our current understanding of computing systems.

There is one thing we can definitely state: Programs produced by an implementation of the right sort will never exhibit absolute OOTA (that is, an OOTA cycle in which all the semantic dependencies are absolute). This is simply because an absolute semantic dependency is *a fortiori* a semantic dependency relative to the compiler in use.

But in fact we have shown more than this: Programs will never exhibit an OOTA cycle relative to the compiler used to build them, even when that cycle is not absolute. In this sense we have gone beyond the requirement of full C++.

#### 6.4.2 Global Analysis and Volatile versus Quasi Volatile

In principle we don't need to require global-analysis compilers to treat atomic objects as volatile; our results would still hold if they merely treated them as quasi volatile. We chose not to do this because it would violate our intuitions about semantic dependencies.

For example, consider the Simple OOTA program, repeated here in simplified form:

```

void thread1() {

int r1 = x;

y = r1;

}

void thread2() {

int r2 = y;

x = r2;

}

```

A loose C++ compiler using global analysis and treating x and y as quasi-volatile objects could omit the two loads, replacing them in the machine code with simple assignments "r1 = 42" and "r2 = 42". This would be a valid transformation, and the resulting behavior would not count as OOTA according to our definition because the dependencies in thread1 and thread2 would not be semantic.

To see why not, recall that a semantic dependency must have a witness, another execution in which the store acts differently. But this transformed program has no other hardware executions; every time it runs it will store 42 to both x and y. (Keep in mind also that since the atomic objects are not treated as volatile, they are not subject to unspecified interference when the program runs in a nonbenign environment.)

This unintuitive behavior could not occur if the two loads were not omitted. In fact, the definition of semantic dependency might remain perfectly acceptable if the requirement for global-analysis compilers were weakened, if the compiler treated atomic objects as quasi volatile and in addition was not allowed to omit accesses to them. This is a possible topic for future research.

## 6.4.3 Effect of Memory Layout

Part of our demonstration of the Fundamental Property of semantic dependencies relies on the fact, stated in Section 3.1, that an abstract execution of a thread is entirely determined by the values obtained for its loads. But when we compare abstract executions of the same thread in two different programs, this may no longer be entirely true owing to the effect of differing memory layouts.

Consider this simple example:

```

x = (int) &x;

```

Even though the example contains no loads at all, it may store different values when running in different programs because the object  $\times$  may be allocated at differing addresses in those programs. According to our definition, this could count as a degenerate OOTA cycle of length one, in which the store is semantically dependent on an empty set of loads!